Issue 10/2006 www.edn.com

**Prying Eyes** undresses NDAS: dissecting a NAS substitute Pg 36

EDN once again looks into the mind of the engineer Pg 12

Innovator of the Year teammate talks about statistical design Pg 28

**Design Ideas** Pg 75

VOICE OF THE ENGINEER

# DESIGNERS CAST A SKEPTICAL EYE ON MIXED-SIGNAL SOCS

Page 48

## HAZARDOUS-VOLTAGE PRIMER

Page 39

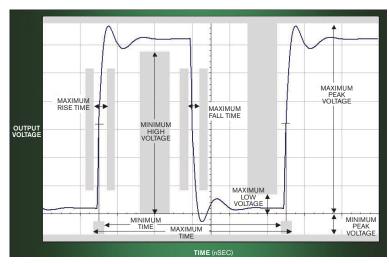

SPREAD-SPECTRUM CLOCKING: measuring accuracy and depth

Page 61

Effective use of IC-amplifier macromodels requires understanding their limitations

Page 69

# PRECISE POWER MANAGEMENT.

#### IT TAKES THE PAIN OUT OF DESIGNING LOW-POWER ICs

Increasing feature, function and processing requirements make it harder than ever to manage power consumption in personal electronics, wireless and handheld devices. A design system that concurrently analyzes and optimizes your IC for power, timing, area, signal integrity and yield is what you need. And that's what Magma provides. Blast Power™ and Blast Rail™NX facilitate significant power reductions throughout the flow, enabling you to complete low-power chips faster. Your design will blow the socks off your competitors' chips but won't blow your power budget, or your schedule.

For more on how Magma lets you get the most out of your chips with just the right amount of power, visit **www.magma-da.com/4LowPower**. Find out why the world's top chip companies rely on Magma software to design their most critical ICs.

# WORLDWIDE SELECTION PERSONALIZED SERVICE

Access to over **540,000** part numbers from more than **320** quality, name-brand manufacturers!

#1 for Breadth of Product

**#1 for Availability of Product**

**#1 for On-Time Delivery**

**#1 for Overall Performance**

Source: EE Times Distributor Evaluation Study, September 2005

CORPORATION

1.800.344.4539

AME-DAY HIPMENT

www.digikey.com

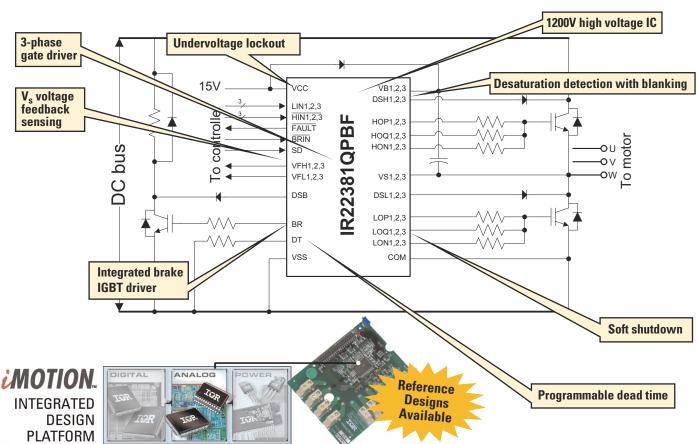

# RUGGED 1200V ICs DRIVE AND PROTECT YOUR MOTOR

High Voltage ICs Provide Dedicated, Reliable Industrial Solution

| Inverter Power                                | <31            | kW             | >3kW               |                    |  |  |

|-----------------------------------------------|----------------|----------------|--------------------|--------------------|--|--|

| Specifications                                | IR2233xPbF     | IR22381QPbF    | IR2213SPbF         | IR22141S           |  |  |

| Configuration                                 | 3-phase driver | 3-phase driver | half-bridge driver | half-bridge driver |  |  |

| Voltage                                       | 1200V          | 1200V          | 1200V              | 1200V              |  |  |

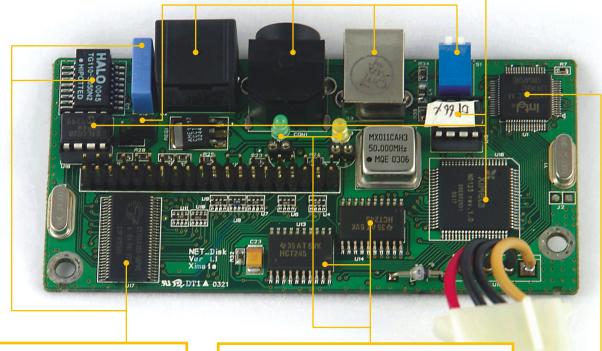

| Dead time (DT)                                | 250ns          | 1µs            | N/A                | 330ns              |  |  |

| Soft shutdown duration time                   | No             | 6.0µs          | No                 | 9.25µs             |  |  |

| t <sub>on</sub> /t <sub>off</sub>             | 750/700ns      | 550/550/ns     | 280/225ns          | 440/440ns          |  |  |

| Matching delay                                | No             | 100ns          | 30ns               | 75ns               |  |  |

| Drive Current I <sub>0+</sub> / <sub>0-</sub> | 190mA/380mA    | 220mA/460mA    | 2.0A/2.5A          | 2.0A/3.0A          |  |  |

| Desaturation<br>blanking time                 | No             | 4.5µs          | No                 | 3µs                |  |  |

| Independent half-<br>bridge driver            | Yes            | No             | Yes                | No                 |  |  |

| Undervoltage lockout                          | Yes            | Yes            | Yes                | Yes                |  |  |

| Integrated brake driver                       | No             | Yes            | No                 | No                 |  |  |

iMOTION is a trademark of International Rectifier.

#### FEATURES

- High and low side gate driver IC

- Integrates low voltage driver with high voltage level shifter

- IR industry leading, high voltage technology

- Single, rugged, compact IC

IR's *iMOTION* brings digital controllers, analog stage and power modules together in one easy to implement, integrated design platform.

International

Rectifier

THE POWER MANAGEMENT LEADER

Don't let poor performance spoil your designs. With high performance AVR® microcontrollers you can create applications with no worries about the microcontrollers performance. AVR Flash microcontrollers operate with clock rates up to 20 MHz, achieving close to 20 MIPS. With 32 general purpose registers, the AVR delivers unmatched performance and flexibility while reducing power consumption to a minimum.

Learn more and try to unmask the Super AVR at www.atmel.com/ad/superAVR

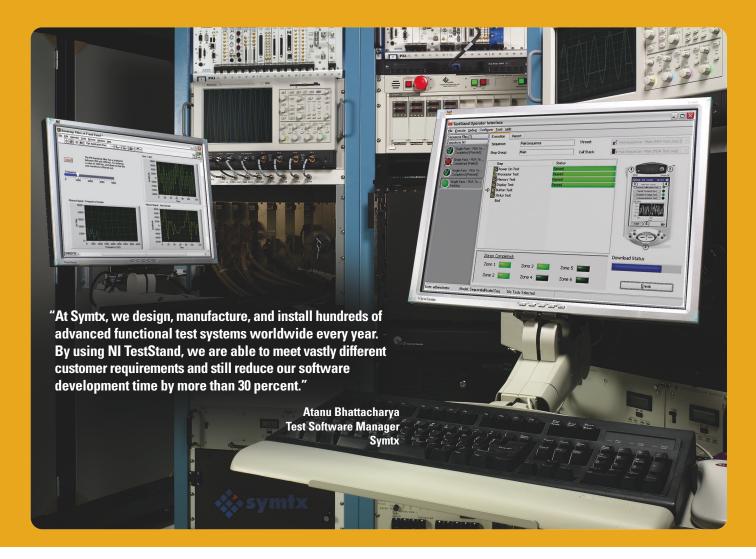

# NI TestStand – The Industry Standard in Test Management Software

NI TestStand is a ready-to-run test management environment from National Instruments for automating your test and validation systems. With NI TestStand you can:

- Develop, manage, and automate your test sequences

- Simplify your maintenance through a modular, fully customizable test-system framework

- Leverage toolkits and add-ons from NI TestStand product and solution partners

- · Execute test modules written in any programming language

- Specify sequence flow, reporting, database logging, and connectivity to enterprise systems

- Maximize test throughput with built-in parallel and batch execution and synchronization

To learn how Symtx and other electronic manufacturers are accelerating development and reducing costs, visit **ni.com/teststand**.

(800) 891-8841

# VOICE OF THE ENGINEER 50 years

# contents

5,11,06

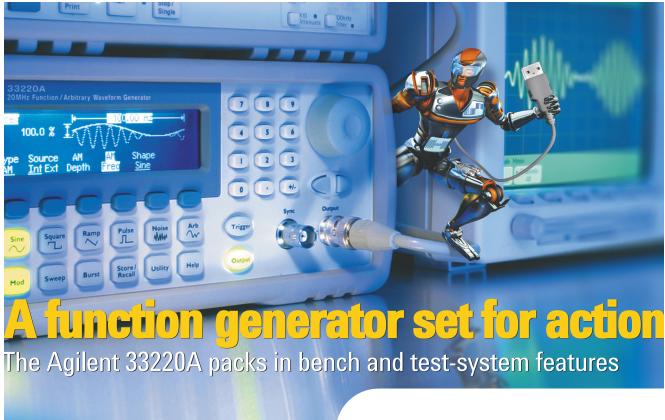

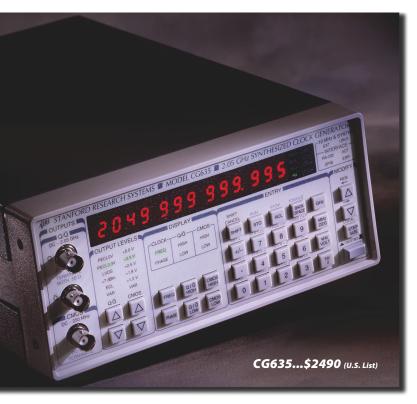

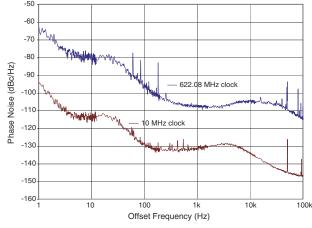

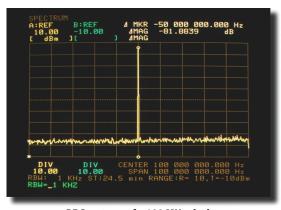

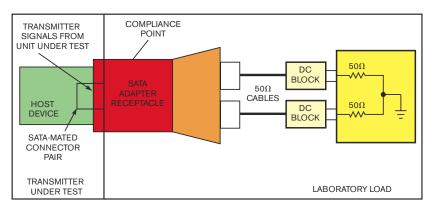

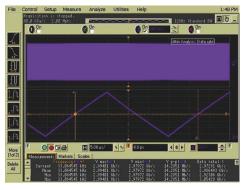

# Spread-spectrum clocking: measuring accuracy and depth

Designers use datarate smearing to spread EMI across multiple frequency bands. Learn how to quickly test and verify your implementation. by Bryan Kantack, Agilent Technologies

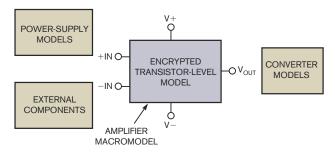

# implementation. by Brya Agilent Te Effective use of IC-amplifier

# macromodels requires understanding their limitations Until IC manufacturers provide users with amplifier macromodels

provide users with amplifier macromodels that are as detailed as those that device designers use, you must make do with less detailed models and an understanding of their limitations.

by Reza Moghimi,

Analog Devices

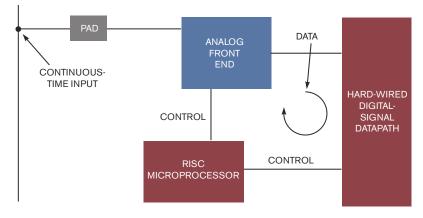

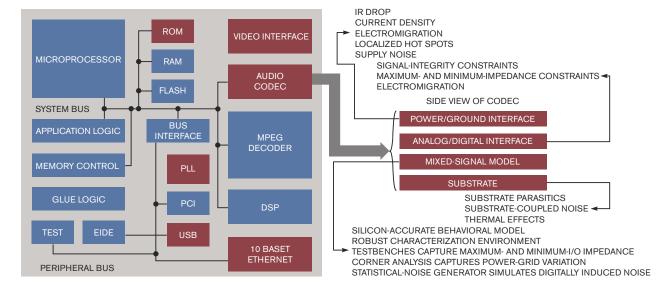

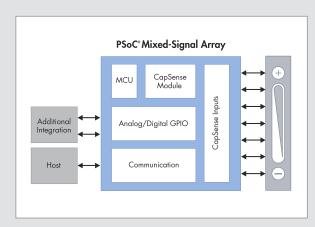

# Designers cast a skeptical eye on mixed-signal SOCs

The functions are necessary, but integration challenges keep analog IP out of the mainstream for SOC design.

by Ron Wilson, Executive Editor

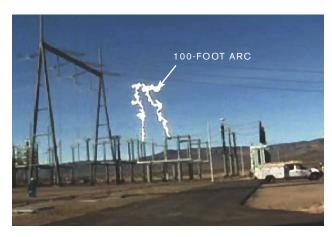

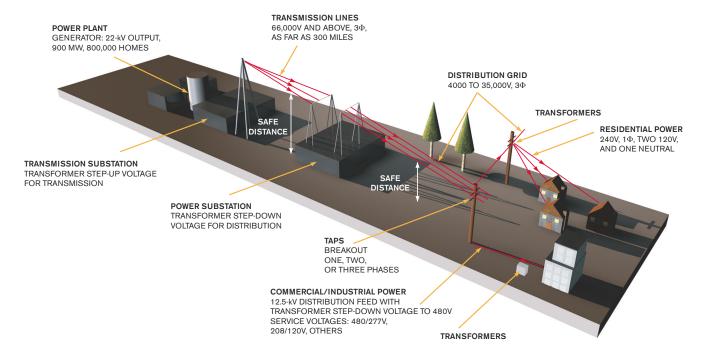

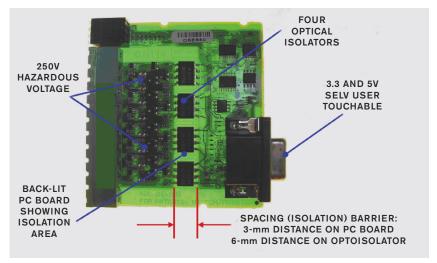

# Hazardous-voltage primer

Understanding the hazards associated with voltage and knowing the principles of safety and the importance of certification are the keys to safe design and product use. Even low voltage is hazardous and can damage products and harm users.

by David Lohbeck,

National Instruments

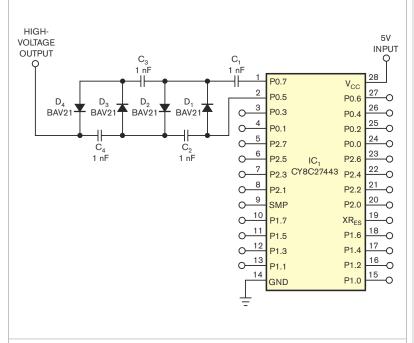

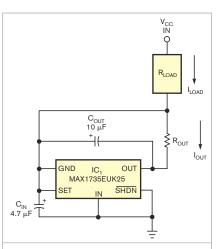

## DESIGNIDEAS

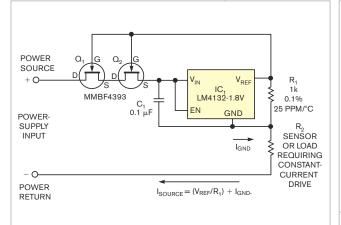

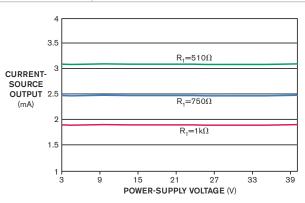

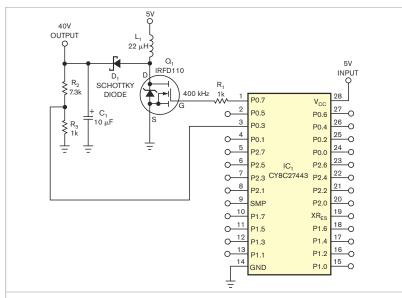

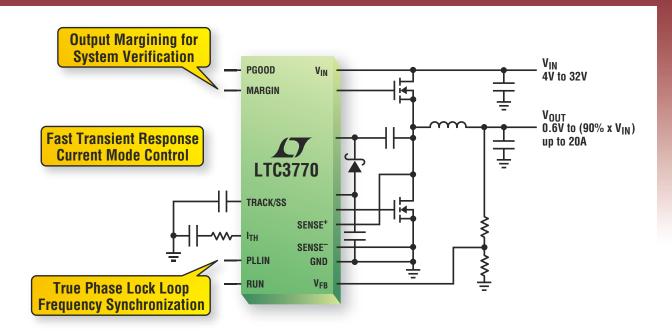

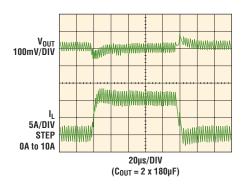

- 75 JFET cascode boosts current-source performance

- 76 Microcontroller delivers voltage-multiplied dc power

- 80 Low-dropout linear regulators deliver constant currents

- Send your Design Ideas to EDNdesignideas@reedbusiness.com.

| Hasii. | V850 32-Bit All Flash Lineup |             |           | 48 KB |         |      | 48KB  |

|--------|------------------------------|-------------|-----------|-------|---------|------|-------|

| 640 KB |                              |             |           | GC    |         |      | GJ    |

|        |                              |             |           | 40 KB | 2       | 0 кв | 40 KB |

| 512 KB |                              |             |           | GC    |         | GJ   | GJ    |

|        |                              |             |           | 32 KB | ★2      | 0 кв | 32 KB |

| 384 KB |                              |             |           | GC/GF |         | GJ   | GJ    |

|        |                              | 12 KB 12 KB | 16кв 12кв | 24KB  | 16 KB 1 | 2 KB | 24KB  |

| 256 кв |                              | GC GK       | GC/GF GC  | GC/GF | GJ      | GJ   | GJ    |

|        | 4KB 6KB                      | 6кв 12кв    | 6кв 12кв  | 12 KB | 6KB 1   | 2 KB | 12 KB |

| 128 KB | GB GB                        | GC GK       | GC/GF GC  | GC/GF | GJ      | GJ   | GJ    |

|        | 6кв                          | 12 KB       |           |       |         |      |       |

| 64 KB  | GB                           | GK          |           |       |         |      |       |

|        | Pin Count: 64                | 80          |           | 100   |         |      | 144   |

- = V850ES/**Kx2** (2.7V to 5.5V operation) = V850ES/**Hx2** (5V with up to 24 channels of 10-bit A/D) = V850ES/**Jx2** (3V high performance) KB = RAM Size ★ = 376 KB Flash Memory

**GB= GK= GC= GF= GJ=** 10x10 mm 12x12 mm 14x14 mm 14x20 mm 20x20 mm

These V850™ flash microcontrollers are fully equipped to take on whatever your mission entails.

- · High performance real-time microcontrollers with high throughput

- · Low power consumption with flexible power management

- · Exceptional EMI/EMS performance

- · All flash product lineup with a wide range of memory sizes and packages

Put a V850 device in your next design. Learn more at www.am.necel.com/28mcus and get an evaluation kit for just \$49 (limited time offer).

### contents 5.11.06

- 23 Fabless-ASIC company tries new model

- 23 Compact controller eases embedded-system motion

- 24 Software reduces cell-phone-test time by nearly an order of magnitude

- 26 DFM tools help with "lithography-friendly" layouts

- 26 Process yields custom boards in five days

- 28 **Voices:** Chandu Visweswariah and IBM innovation bring statistics to digital-IC design

- 30 **Global Designer:** MEMS microphone has digital output; Spin-coating process produces TFT with liquid silicon; Consortium invests \$800,000 for five years

## DEPARTMENTS & COLUMNS

- 12 **EDN.comment:** Mind of the engineer

- 34 Baker's Best: Charge your SAR-converter inputs

- 36 Prying Eyes: NDAS undressed: dissecting a NAS substitute

- **Reality Check:** Wireless protocol lags initial expectations

## PRODUCT ROUNDUP

- Sensors & Transducers: LVDT-based position sensors, MEMS-based sensors, current-sensing ICs, and more

- 89 Embedded Systems: Hybrid embedded boards with a four-DSP processing cluster, I/O modules for solid-state relays, switcher/router cards, and more

EDN® (ISSN#0012-7515), (GST#123397457, RBL Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 51, Number 10 (Printed in USA).

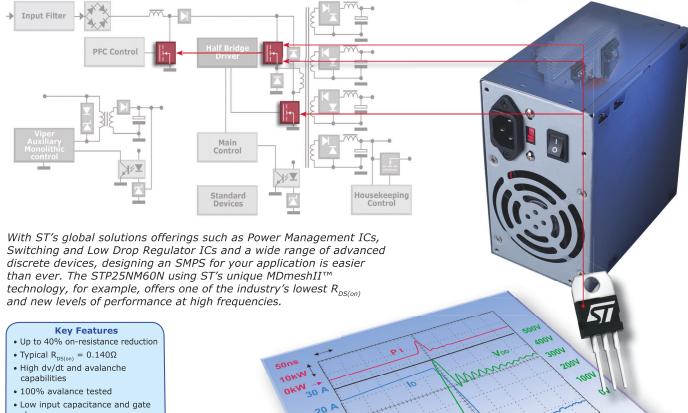

# **Power Supply & Management**

MDmeshII Power MOSFETs with super-low R<sub>DS(on)</sub> give even lower power losses and easier driving for all your high-frequency SMPS applications.

Innovative products for multi-segment application systems

- charge

- Low gate input resistance

| Part<br>Number (0 | V <sub>DSS</sub><br>@Tjmax) | R <sub>DS(on)</sub> | $I_{D}$ | Pkge.              |

|-------------------|-----------------------------|---------------------|---------|--------------------|

| STB25NM60N-1      | 650V                        | < 0.170Ω            | 20A     | I <sup>2</sup> PAK |

| STF25NM60N        | 650V                        | < 0.170Ω            | 20A*    | TO-220FP           |

| STP25NM60N        | 650V                        | < 0.170Ω            | 20A     | TO-220             |

| STW25NM60N        | 650V                        | < 0.170Ω            | 20A     | TO-247             |

| STB25NM60N        | 650V                        | < 0.170Ω            | 20A     | D <sup>2</sup> PAK |

<sup>\*</sup> Limited only by maximum temperature allowed

For datasheets, application notes and more information visit www.st.com/mdmesh

MDmeshII is a trademark of STMicroelectronics.

# EDN online contents www.edn.com

#### **ONLINE ONLY**

Check out these online-exclusive articles.

#### ZigBee chip project offers SOC challenges

Design decisions: Geographically dispersed engineering team takes on integration of internal and third-party IP for RF

www.edn.com/article/CA6325290

### USB-hub chip accepts hospitality of two hosts

The device enables a single USB hub to furnish not one but two host systems with access to a set of attached peripherals.

www.edn.com/article/CA6325520

#### Good engineers are worriers

The 2006 Electronic Design Processes Workshop did an admirable job of putting many of the industry's worries on the table.

> www.edn.com/article/CA6326107

### Offerings advance audio at home, on the road

New additions to the toolbox include DSPs for low-cost home and automotive systems and a certified design for home-based HD Radio receivers.

> www.edn.com/article/CA6324252

### Guest opinion: Will the real ESL please stand up?

The industry is still waiting for a truly disruptive technology to become the universally acknowledged design methodology.

www.edn.com/article/CA6326108

## **EDN's 2006 Digital Signal** Processing Directory

www.edn.com/dspdirectory

Check out Technical Editor Robert Cravotta's annual directory of DSP devices and cores—an easy-to-browse yet exhaustive resource that features:

- Robert's incisive summary of every product family from every vendor

- Tons of downloadable PDF tables that allow you to zoom in on the DSP resources you need for your design

- Downloadable architectural block diagrams

- A sidebar ("Where did they go?") that helps you track where certain DSP offerings have ended up by virtue of acquisitions and other vendor moves.

#### FROM THE VAULT

Items from the EDN archives that relate to this issue's contents.

DESIGNERS CAST A SKEPTICAL EYE ON MIXED-SIGNAL SOCs (pq 48):

Enabling analog-IP reuse: relating requirements to reality

→ www.edn.com/article/CA409045

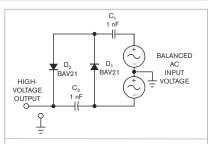

## HAZARDOUS-VOLTAGE PRIMER (pg 39):

Circuit-protection methods yield more robust products (includes some explosive video clips)

→ www.edn.com/article/CA514947

Safety isolation protects users and electronic instruments

→ www.edn.com/article/CA454635

#### SPREAD-SPECTRUM CLOCKING: MEASURING ACCURACY AND DEPTH (pg 61):

Engineers still suffering from jitter jitters

→ www.edn.com/article/CA6305400 12.5-Gbps serial BERT characterizes

jitter

→ www.edn.com/article/CA6279640

#### **READERS' CHOICE**

A selection of recent articles receiving high traffic on www.edn.com.

### Tackle noise from three perspectives

You've got noise in your circuit? Where do you look to find it?

> www.edn.com/ article/CA6321523

### End of memory relationship may impact

www.edn.com/article/CA6321526

deliver gate-drive pulses with rise and fall

ideal candidates for laboratory pulse gen-

times of less than 2 nsec, making them

erators.

M-Systems and Samsung's parting of ways may have huge implications for highend cell phones.

www.edn.com/article/CA6324003

### Design Idea: Isolated-FET pulse driver reduces size, power consumption

Drive a capacitive-input power device with any duty cycle at frequencies to 200 kHz.

→ www.edn.com/article/CA6317069

# This simple method uses only digital logic and fixed-value resistors. > www.edn.com/article/CA6321527

Design Idea: Shift registers and resistors

deliver multiphase sine waves

## Design Idea: Use a switching-regulator controller to generate fast pulses

Switching-regulator-controller ICs can

© Koninklijke Philips N.V., 2005. All rights reserved.

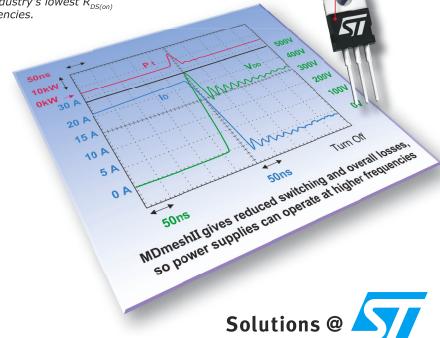

#### **High-Performance Low-Cost Solution.**

**32-bit Flash Microcontrollers.** The Philips LPC210x ARM7TDMI-S<sup>™</sup>-based MCU can help you with your application challenges by providing you with the industry's fastest ARM7-based microcontroller.

#### An easy upgrade path, minimal relearning

#### Single-chip solution with lots of peripherals

- On-chip Flash

- -Timers, PWM, UARTs, SPI/SSP, I<sup>2</sup>C

- -ADC

- Predictable, deterministic performance

- No cache required

- Same performance between Flash and RAM code execution

#### Low power for battery-operated applications

- < 10uA power down, < 1 mW/MHz active

Fast I/Os to implement interfaces, handshaking functions in software

High-performance 32-bit solutions at 8-bit MCU pricing

Highly reliable Flash memory

Low-cost tools support

For more information, please visit www.philips.com/microcontrollers

# Support Across The Board.

Starting with in-depth design support all the way through to total supply chain management – Avnet Electronics Marketing is there for you.

From concept to reality, we deliver:

Consultative engineering support and services

Focused product specialization

The broadest supplier partnerships in the industry

Over \$1 billion in top moving inventory "on the shelf"

World-class supply chain services

But, partnering with Avnet Electronics

Marketing means much more than just

having access to the industry's broadest

array of design and supply chain services.

It means working with a company that is truly

focused on exceeding your needs and

expectations – a company that is dedicated

to giving you Support Across The Board."

Ready.

Set.

Go to market.™

Enabling success from the center of technology ™

1 800 332 8638 www.em.avnet.com

#### BY MAURY WRIGHT. EDITOR IN CHIEF

## Mind of the engineer

recently wrote about our commitment to serving the reader and, briefly, our belief in perpetual research to measure our performance and to understand our readers (**Reference 1**). In this issue, I share some recent research with you. Every two years, we do a major study, "Mind of the Engineer." The early results are back from the latest incarnation.

This year, we fielded the study worldwide and have statistically valid results from North America, Europe, China, Japan, and other parts of Asia. Almost 50% of the respondents are design-and-development engineers, and most of the rest split between pure R&D and engineering management. The results that I present here are specific to North America except where noted.

Let's start with what you indicate to be your greatest challenges today. Number one on the list is keeping up with the latest technologies. Other top mentions include shorter design cycles, outsourcing/offshore concerns, and working with fewer resources. Here's one direct response: "It is a must to keep current with the world, even if it does not directly affect me at this time." I suppose none of the responses is a surprise. You can perhaps take solace in knowing that you don't face them alone.

We asked how many projects you work on over the course of a year. Nine is the average, although those of you working in the consumer and computer segments reported 10 and 11, respectively. Numbers from other regions are generally lower; engineers in China work on only five projects per year. In North America, the automotive segment stands out; those working in that segment report that they work on 17 projects a year. I'd like to better understand that number. Perhaps it's due to the fact that engineers in the automo-

Clearly, you face pressure to excel in multiple design disciplines, with 58% reporting an increase over the past two years.

tive segment have more overlapping long-term projects. Generally, almost all respondents report working on more projects now than in the past.

The study also reveals an increase in the number of you that work in teams—a trend that continues from past Mind of the Engineer studies. Today, 48% report working on teams, although the figure zooms to 62% for engineers under the age of 39.

For those of you actively working in teams, 31% have team members outside North America. More of those team members are in Western Europe than elsewhere, but 36% report work-

ing with team members in China, 26% in India, 19% in Taiwan, and 12% in Japan.

We also asked about how you divide your time at work and what increased responsibilities you have assumed. Clearly, you face pressure to excel in multiple design disciplines, with 58% reporting an increase over the past two years. With thin resources, analog specialists must be able to handle some digital work. We've found that FPGA designs have become the province of software specialists. I don't expect the trend to end.

Most of you—81%—also now support your designs through manufacturing. That number is fairly consistent worldwide with the exception of Japan, where only 39% of respondents support their designs through manufacturing. One North American engineer states, "The greatest challenge for me has been to deal with the expanding scope of the design-engineering process. Besides the basic engineering functions, I have had to become knowledgeable in all phases—from initial concept to manufacturing."

You also have to tolerate the fragility of the product-development process. On average, only 59% of your projects reach the market. The number of canceled projects soared in the 2000-to-2002 time frame, but I am frankly surprised that the success rate isn't higher today. The numbers are fairly consistent across application segments, as well. And only Europe stands out globally with only 45% of projects making it to market.

I'd like to thank all of you who participated in the study. We truly value your input. I welcome comments and questions. E-mail mgwright@edn.com, call 1-858-748-6785, or comment in the "Feedback Loop" in the online presentation of this column.

#### REFERENCE

Wright, Maury, "Serving you: the *EDN* mission," *EDN*, April 13, 2006, pg 14, www.edn.com/article/CA6321530.

# If you're doing POL or VRM, check out our SLC, MVR, MLC or SER.

**SLC7530** 0.05 - 0.4 µH Up to 50 A 6.7 x 7.5 mm 3 mm high

**SLC7649** 0.04 - 0.1 µH Up to 100 A 7.5 x 7.6 mm 5 mm high

**SLC1049** 0.08 - 0.15 μH Up to 61 A

6.9 x 10.2 mm

5 mm high

**MVRT** 0.25 -0.56 μH Up to 35 A 9.8 x 11.5 mm 5.1 mm high

**MVRC** 0.36 - 2.3 µH Up to 36 A 9.8 x 11.5 mm 4.7- 7.8 mm high

VRC MLC12 - 2.3 µH 0.36 - 4 o 36 A Up to 37 11.5 mm 10.5 x 11.2

MLC1200 MLC1500 0.36 - 4 μH 0.5 - 4.5 μH Up to 37 A Up to 32 A 10.5 x 11.2 mm 13.2 x 13.8 mm 4.1 - 6.1 mm high 3.9 - 6.5 mm high

1**1500 SER** 4.5 µH 0.33 -5 32 A Up to 13.8 mm 13.1 x

**SER1360** 0.33 - 10 μH Up to 48 A 13.1 x 12.9 mm 5.8 mm high

**SER 1590** 0.3 - 1 μH Up to 50 A 16.3 x 15.8 mm 10.2 mm high

**SER2000** 0.3 - 2 μH Up to 100 A 19.6 x 20.1 mm 8.6 - 14 mm high

# And get samples PDQ.

Only Coilcraft offers such a broad range of high current, low DCR power inductors.

They're perfect for Point of Load and Voltage Regulator applications. Or any place you need maximum current handling in minimum space.

Several models are rated up to 100 A rms. Others have powdered iron cores for maximum saturation current and minimum thermal aging.

Still others offer 5% DCR tolerance, making them ideal for current sensing applications.

As always, you can get free evaluation samples from our web site with just a click of the mouse. We ship same day!

Check out our full line of POL and VRM magnetics ASAP. Visit www.coilcraft.com/POL3

#### **NEXXIM®**

Time and frequency-domain circuit simulation to predict multi-gigabit channel performance including S-parameters and transistor-level effects of drivers and receivers

#### HFSS™/Q3D EXTRACTOR®

GHz-accurate S-parameter and Full-Wave Spice<sup>™</sup> models for complex trace routing, vias and transitions, connectors and IC packages

#### **SIWAVE™**

Full-board and full-package interconnect extraction for signal and power-integrity analysis

#### **DESIGNERSI**<sup>™</sup>

System-level signal integrity analysis with dynamic links to Nexxim and HFSS

# FRAM memory for high-speed data collection

FRAM memory is optimized for nonvolatile data storage in a wide variety of applications. FRAM writes as fast as it reads, it's nonvolatile, and offers virtually unlimited write cycles. No algorithms or protocols are needed to write data and FRAM is byte addressable like SRAM.

System designers are putting the advantages of FRAM to work in a broad range of system applications from industrial equipment to plasma and LCD televisions. FRAM memories are also collecting data for world's largest digital utility meter installation and are storing data in some of the finest automobiles.

Find out

how FRAM

memory can raise

the standard in your next

design by calling a Ramtron

technical engineer at 1-800-5453726 or simply e-mail

framinfo@ramtron.com

Download a Free FRAM Short Form Catalog today at www.ramtron.com.

#### FM20L08 - 1-Megabit FRAM Memory

- SRAM compatible JEDEC 128Kx8 SRAM pinout

- 60ns access time & unlimited read/write endurance

- True nonvolatile RAM no battery required

- Low power 3-volt operation

- Significant board space savings 32 pin TSOP

www.ramtron.com

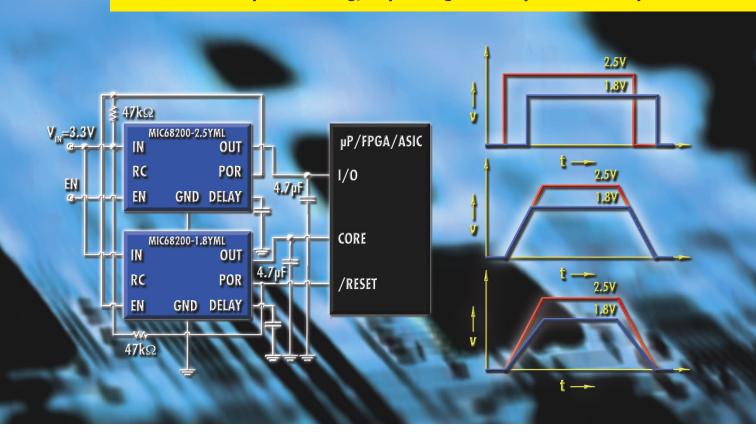

# **Get on Track with Micrel Sequencing**

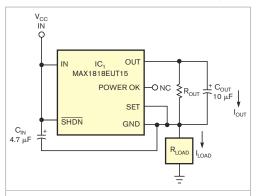

MIC68200 Solves your Tracking, Sequencing and Ramp Control™ Requirements

ASIC, FPGA and CPU manufacturers require complex and unique start-up protocols for loads on the system board. Micrel's MIC68200 is designed specifically to address those protocols and make the task of the system designer simpler.

The MIC68200 operates from a wide input range of 1.65V to 5.5V, which includes all of the main supply voltages commonly available today. It is designed to drive digital circuits requiring low voltage at high currents. The chip incorporates a delay pin (Delay) for control of power on reset output (POR) at turn-on and power-down delay at turn-off.

Additionally, there is a ramp control pin (RC) for either tracking applications or output voltage slew rate adjustment at turn-on and turn-off. This is an important feature in applications where the load is highly capacitive and in-rush currents can cause supply voltages to fail and microprocessors or other complex logic chips to hang up. All power-up protocols, sequencing, window sequencing, tracking and ratiometric tracking can be implemented with minimal components, thereby eliminating the need for complex power management ICs.

For more information, contact your local Micrel sales representative or visit Micrel at: www.micrel.com/ad/mic68200. Literature 1 (408) 435-2452 Information 1 (408) 944-0800

#### The Good Stuff:

- ◆ Input voltage range: 1.65V to 5.5V

- Stable with 4.7μF ceramic capacitor

- ◆ 1.0% initial output tolerance

- ◆ 2A maximum output current peak start up

- ◆ 1A Continuous Operating Current

- Power-on Reset (POR) supervisor with programmable delay time

- Programmable Ramp Control for in-rush current limiting and slew rate control of the output voltage

- ◆ Tracking on turn-on and turn-off with pin strapping

- ◆ Timing Controlled Sequencing On/Off

- Single Master can control multiple Slave regulators

www.micrel.com

# ANALOG edge<sup>ss</sup>

Expert tips, tricks, and techniques for analog designs

Vol. IV, Issue 5

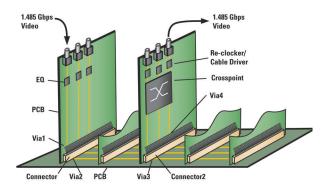

# Overcoming Impedance Discontinuities in High-Speed Signal Paths by Using LVDS

by Brian Stearns, Principal Engineer

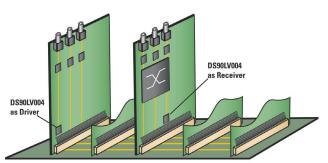

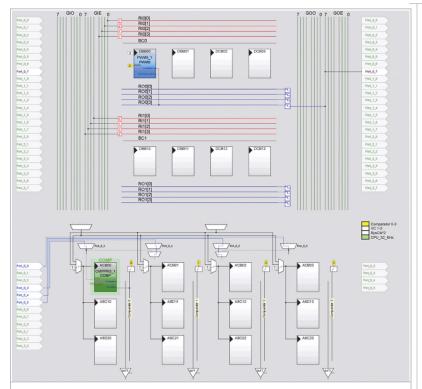

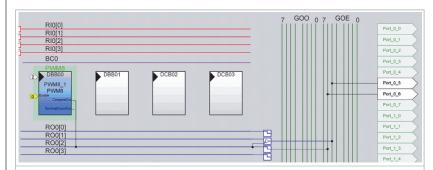

Figure 1. HD Video Router Diagram

t data rates from 400 Mbps to 1.5 Gbps, data signal paths become transmission lines. At these speeds the signal path model must include the reactive parasitic components in the cable or backplane. It is not just the data rate itself—the fast edge rates contain even higher frequency energy that react worse in distributed impedance environments. Ignoring parasitic impedances and impedance discontinuities above 200 Mbps will cause added noise in the transmission line, and data bit errors will occur.

Consider a basic High-Definition (HD) digital video router as an example of this challenge: HD video routers manage multiple HD source streams for distribution in broadcast, studio, or production video facilities. HD video channels operate from 270 Mbps up to 1.485 Gbps, demanding careful layout and consistent design practices to ensure the switching router system does not degrade the integrity of the video data.

In this system (*Figure 1*), an Adaptive Equalizer (EQ) receives the HD signal directly from the BNC connector.

A common backplane connects the signals from the input card to the switch card for output to the desired destination channel. The signals travel point-to-point from the EQ across the PCB approximately 8 inches to the backplane connector, then across ~3 to 15 inches of backplane (depending on the slot used) to a second connector, then across another 8 inches of PCB to the inputs of the crosspoint switch device. A re-clocker/cable driver connects directly to the outputs of the crosspoint switch to drive the signals across cables. These HD video router systems are modular and may have anywhere from 8 to 1000 input/output channels. Therefore, signal density can be very high.

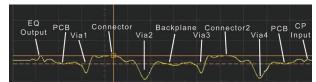

Figure 2. Example TDR Plot of Impedance Across the Signal Path (See *Figure 1* for discontinuity locations)

The common FR4 circuit board materials are a consistent impedance environment, but the distributed parasitic impedances will have a negative effect on the signal quality. Most affected are the fast edge rates as a result of the numerous frequency components operating higher than the fundamental data rate, causing signal losses and sluggish transition times. In addition, all the interconnections between the components (such as the BNC connectors, integrated circuits, vias between board layers, or the connectors between boards) can cause impedance mismatches from the characteristic impedance (Z<sub>0</sub>), which will also affect signal quality (*Figure 2*). The dense backplane connectors inductively load the signal path,

**Voltage-Controlled Filter**

#### **Featured Products**

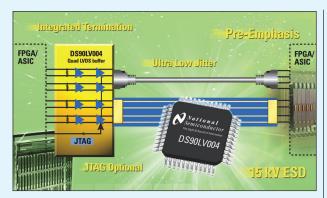

#### **Four-Channel LVDS Repeater with Pre-Emphasis**

The DS90LV004 is a four channel 1.5 Gbps LVDS buffer/repeater. High-speed data paths and flow-through pinout minimize internal device jitter and simplify board layout, while configurable pre-emphasis overcomes ISI jitter effects from lossy backplanes and cables. The differential inputs interface to LVDS, and Bus LVDS signals such as those on National's 10-, 16-, and 18- bit Bus LVDS SerDes, as well as CML and LVPECL. The differential inputs and outputs are internally terminated with a  $100\Omega$  resistor to improve performance and minimize board space. The repeater function is especially useful for boosting signals for longer distance transmission over lossy cables and backplanes.

#### **Features**

- Hot-plug protection

- LVDS/CML/LVPECL compatible input, LVDS output

- On-chip  $100\Omega$  input and output termination

- 15 kV ESD protection on LVDS inputs and outputs

- Single 3.3V supply

- Very low power consumption

The DS90LV004 operates over a wide temperature range (-40 to +85°C) making it ideal for telecom, datacom, industrial, medical, automotive, and office imaging applications applications. It is available in a TQFP-48 package.

For FREE samples, datasheets, and more, visit www.national.com/pf/DS/DS90LV004

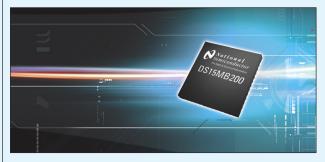

## Dual 1.5 Gbps 2:1/1:2 LVDS Mux/Buffer with Pre-Emphasis

The DS15MB200 is a dual-port 2 to 1 multiplexer and 1 to 2 repeater/buffer. High-speed data paths and flow-through pinout minimize internal device jitter and simplify board layout, while pre-emphasis overcomes ISI jitter effects from lossy backplanes and cables. The differential inputs and outputs interface to LVDS or Bus LVDS signals such as those on National's 10-, 16-, and 18- bit Bus LVDS SerDes, or to CML or LVPECL signals

#### **Features**

- 1.5 Gbps data rate per channel

- Configurable off/on pre-emphasis drives lossy back planes and cables

- Low output skew and jitter

- On-chip  $100\Omega$  input and output termination

- 15 kV ESD protection on LVDS inputs/outputs

- Hot-plug protection

The DS15MB200 features a 3.3V supply, CMOS process, and robust I/O ensure high performance at low power over a wide temperature range (-40 to +85°C) making it ideal for base-stations, DSLAMs, routers, switchers, and industrial systems applications. It is available in LLP-48 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/DS/DS15MB200

#### **Overcoming Impedance Discontinuities in High-Speed Signal Paths by Using LVDS**

while vias in the PCB capacitively load the signal path. Signal reflections will occur at any location along a transmission path where a change in impedance exists. These reflections and parasitic impedances will cause loss of signal amplitude, ringing, rise time degradation, and EMI.

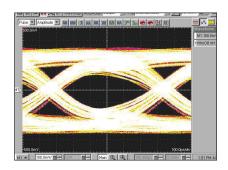

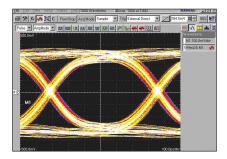

In this example system there can be up to 31 inches of FR4 from the EQ outputs to the input of the crosspoint switch, with several impedance discontinuities along the way. If the speed of the incident edge is 175 to 200 ps/inch down this path, and the data rate is 1.485 Gbps (half-wavelength = 343 ps), then there can be as many as 18 transitional edges on the path at any given time. Reflections caused by the incident edge at impedance mismatches will affect all the edges present on the signal path. Reflections from edges 1 through 17 will greatly distort edge number 18 by the time it arrives at the end of the signal path. The resulting eye pattern (*Figure 3*) shows the loss of amplitude, excessive jitter, and rise/fall time degradation.

Figure 3. Eye Pattern at Input to Crosspoint Switch After 31" of FR4

One possible solution to this challenge is to use higher quality connectors between the daughter cards and the backplane. This will minimize the discontinuities of the connectors. Better via design will further flatten the TDR measurement plots so that the apparent impedance over the length of the signal path stays much closer to  $Z_0$ .

Figure 4. Buffer Locations to Overcome Impedance Discontinuities

Another, more cost-effective solution is to use a simple LVDS buffer, such as the DS90LV004, to drive and receive the signal across the backplane. This effectively breaks the transmission path into smaller segments to mask the impedance mismatch and diminish signal attenuation. Place a buffer at the edge of the daughter card to drive the connector and backplane, a second buffer on the switch daughter card to receive the signals (*Figure 4*), and re-drive them to the input of the crosspoint switch to effectively hide the impedance discontinuities between the two buffers (*Figure 5*). Proper terminations also ensure that the receiver absorbs all the energy in the line and none reflects back to the source.

Figure 5. Eye Pattern at the Crosspoint Input with DS90LV004 Buffers

Isolating the Backplane Connections

In addition, the buffers typically offer additional signal quality enhancements to improve the original signal. For example, buffers featuring input equalization will remove the deterministic jitter from the media losses before delivery across the backplane. Output pre-emphasis can boost the amplitude of the signal, further opening the eye pattern at the crosspoint inputs or receiver. High ESD ratings on the buffer I/O protect the other components on the daughter cards from ESD events elsewhere on the backplane.

#### **Summary**

High-speed interfaces across backplanes require impedance control along the entire signal path. Using simple LVDS buffers to isolate impedance discontinuities or to shorten the interconnect lengths can reduce system costs and enhance the interface performance by eliminating the need for expensive high-frequency connectors.

Sign-up for email alerts of new issues at edge.national.com

#### **Featured Products**

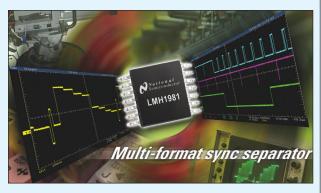

#### **Multi-Format Video Sync Separator**

The LMH1981 is a multi-format sync separator for high-definition broadcast and professional video systems. The device automatically detects the input video format and performs all the necessary sync separation to generate low-jitter horizontal and vertical sync signals for standard and high-definition video formats, including NTSC, PAL, SECAM, 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p.

The LMH1981 features the timing outputs needed for any video system, including horizontal, vertical and composite sync, odd/even field, burst/back porch clamp, and a patented automatic video-format detection feature. The device accepts both bi- and tri-level sync video inputs and features 50% slicing to ensure accurate separation of signals that vary in amplitude, offset, and noise. The device has a wide input range, allowing the inputs to accept video signals from 500 mV<sub>P-P</sub> to 2 V<sub>P-P</sub>.

#### **Features**

- 50% Sync slicing

- Low jitter horizontal sync outputs

- Supports NTSC, PAL, SECAM, 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p

- Accepts video signals from 500 mV<sub>P-P</sub> to 2 V<sub>P-P</sub>

- No external programming with μC required

- Horizontal sync output propagation delay <50 ns</li>

The LMH1981 is ideal for use in a wide range of video applications such as, broadcast video equipment, video distribution, DTV and HDTV systems, and is available in TSSOP-14 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH1981.html

## **Analog Crosspoint Switches for High-Resolution Video Applications**

The LMH® family of high speed amplifiers is joined by the LMH6582 and LMH6583 16 x 8 analog crosspoint switches. The devices are available in a gain of 1 (LMH6582) and gain of 2 (LMH6583) options and are completely non-blocking. Allowing an output to be connected to any input, including an input that is already selected. The devices can be used in distribution applications where each output is connected to the same input, also known as broadcast mode. The inputs and outputs are also fully-buffered, allowing impedance matching to any source at the inputs and capability to drive up to two back terminated  $75\Omega$  video loads on the outputs.

Designed on National's proprietary VIP10 process, both devices offer significant speed and crosstalk performance over competitive solutions. The 500 MHz of bandwidth and 0.1 dB gain flatness out to 100 MHz support high resolution video formats to QXGA (2048 x 1536) and beyond.

#### **Features**

- 500 MHz, -3 dB Bandwidth

- Fast slew rate: 3000 V/µs

- 100 MHz, 0.1 dB gain flatness

- Low crosstalk:

- -70 dBc at 5 MHz

- -- 50 dBc at 100 MHz

- Gain =1 and gain =2 options available

- Serial programming

The LMH6582 and LMH6583 are ideal for use in wideband routers and switchers, conference room systems, keyboard/video/mouse systems, multimedia video systems, and professional A/V systems. These products are available in a unique TQFP-64 package.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMH6582.html www.national.com/pf/LM/LMH6583.html

#### PUBLISHER,

#### EDN WORLDWIDE John Schirmer

1-408-345-4402; fax: 1-408-345-4400 jschirmer@reedbusiness.com

#### **EDITOR IN CHIEF**

Maury Wright 1-858-748-6785 mgwright@edn.com

#### EXECUTIVE EDITOR

Ron Wilson 1-408-345-4427 ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasey Clark

Contact for contributed technical articles

1-781-734-8436; fax: 1-781-290-3436

kase@reedbusiness.com

#### EXECUTIVE EDITOR, ONLINE

Matthew Miller 1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### EMBEDDED SYSTEMS

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646 wwebb@edn.com

#### ANALOG/COMMUNICATIONS, DISCRETE SEMICONDUCTORS

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### EDA, MEMORY,

PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor;

1-408-345-4424 michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPs, TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070 rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA,

PCs AND PERIPHERALS

Brian Dipert, Senior Technical Editor;

1-916-760-0159; fax: 1-781-734-8038;

bdipert@edn.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

#### DESIGN IDEAS EDITOR

Brad Thompson edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-928-1403; mbutler@reedbusiness.com

#### EDITORIAL AND ART PRODUCTION

Diane Malone, Manager

1-781-734-8445; fox: 1-781-290-3445

Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fox: 1-781-290-3442

Melissa Annand, Newsletter/Editorial Coordinator

1-781-734-8443; fox: 1-781-290-3443

Adam Odoardi, Prepress Manager

1-781-734-8325; fox: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Brashears, Production Manager 1-781-734-8328; fax: 1-781-734-8086 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-781-734-8086 Pam Boord, Advertising Art 1-781-734-8313; fax: 1-781-290-3313

#### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SMZ 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirlimaya Varma, Editor in Chief kirli.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### DENNIS BROPHY

Director of Business Development Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect, Intel

#### RON MANCINI

Staff Scientist, Texas Instruments

#### GABRIEL PATULEA Design Engineer, Cisco

MILLID DAVEL

#### MIHIR RAVEL

VP Technology, National Instruments

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fox: 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

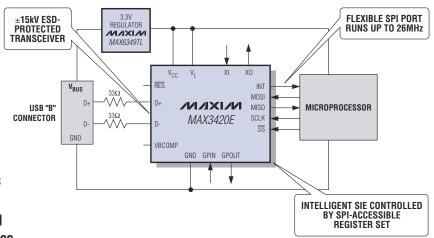

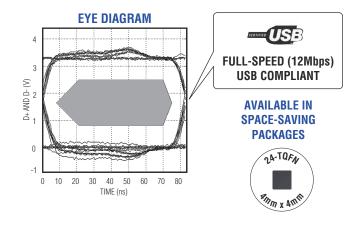

# Simple. Complete. USB Data Acquisition.

## **NI CompactDAQ**

NI CompactDAQ provides the plug-and-play simplicity of USB for sensor, electrical, mechanical, and physical measurements. It delivers fast and accurate data acquisition in a small, simple, and affordable system.

- Hi-Speed USB (2.0) for up to 3.2 MS/s signal streaming

- Multiple connectivity options for sensors and signals

- Hot-swappable modules with built-in signal conditioning

- Simple setup with hardware autodetection

- Driver for National Instruments LabVIEW and text- based languages included

Take a virtual tour of NI CompactDAQ at ni.com/compactdaq.

800 327 9894

© 2006 National Instruments Corporation. All rights reserved. LabVIEW, National Instruments, NI, ni.com, and NI CompactDAQ are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 2006-6881:301-1015.

And Every Step In Between.

From concept to completion, Advanced is your *single* source for comprehensive BGA socketing systems. We specialize in economical, dependable alternatives to direct device attach, with an array of innovative solutions for any stage of development. Whether you're using BGA, LGA or CSP devices in prototype or production applications — you can be sure we're with you every step of the way.

To learn more, visit us online at http://www.bgasockets.com or call 1.800.424.9850.

5 Energy Way, West Warwick, Rhode Island 02893 USA

## Fabless-ASIC company tries new model

aybe the world isn't beating the bushes to find another fabless-ASIC company. But start-up Key ASIC believes that it has a model-an application-specific approach-that's just different enough to make a place for itself beside the relative giants, such as eSilicon (www.esilicon. com) and OpenSilicon (www. opensilicon.com). The company drew its digital engineers from hardware-optimization Arcadia Design company Systems (www.arcadiadesign. com) and its mixed-signal engineers from Intel (www.intel. com). Key ASIC now has two design teams comprising 30 engineers. Half of the members are in Silicon Valley, and half are in Malaysia. Working with a number of independent IP (intellectual-property) companies, the company has built up a portfolio that includes an ARM9 core, high-speed interface IP, audio and video-including HD-ADCs, and power-conversion blocks. The company targets the consumer and wireless-device markets.

The ARM9 illustrates the value added in Key ASIC's approach. Rather than simply pass a synthesizable core through to customers, the company uses customer specs to produce an optimized hard core with the speed, power, and cache configuration the customer needs. Presumably,

the company will take a similar approach to the other critical datapaths in the customer's SOC (system-on-chip) design.

Key ASIC offers two-month turnaround on multidesign wafer-shuttle services, as well as full concept-to-production joint design with the customer. With its roots in Malaysia, the company has insider knowledge of the packaging, testing, and yield-engineering portions of the process. Key ASIC is currently offering 180- and 130-nm CMOS processes from Sil-

Terra (www.silterra.com) and TSMC (www.tsmc.com). Initial customer designs and some of the IP blocks are currently in shuttle runs, and the company expects to have production tape-outs this year.

-by Ron Wilson

▶ **Key ASIC**, www.keyasic.com.

# Compact controller eases embedded-system motion

Targeting medical devices, optical instruments, and embedded-system automation applications, AllMotion recently announced a dual-axis stepper-motor controller and driver. Measuring just 1.6×1.6 in., the EZHR17EN provides as much as 2A of drive current for one axis and as much as 1A for the second with an optional driver daughtercard. The EZHR17EN gives positioning, acceleration, and velocity capability to any stepper motor that is NEMA size 23 or smaller

The EZHR17EN command set is compatible with devices using the Cavro DT or OEM medical-communications protocols, allowing high-speed, complex motion at speeds as high as 20 million microsteps/sec. Using the device, you can issue commands from any serial-terminal program, such as HyperTerminal, or from the EZ Stepper Windows application. With command strings and other programs in the onboard EEPROM, the EZHR17EN can operate stand-alone with no connection to a PC. A single four-wire bus can link as many as 16 stepper-motor controllers in a daisy chain. The EZHR17EN controller sells for \$225, and the daughterboard costs \$69.

AllMotion Inc, www.allmotion.com.

A new, dual-axis stepper-motor controller and driver from AllMotion provides embedded-system designers with precision motion control in a compact package.

## Software reduces cellphone-test time by nearly an order of magnitude

ccording to Agilent Technologies, cellulartelecommunicationsmarket analysts estimate that vendors this year will manufacture 800 million to 1 billion cell phones. Moreover, although many US customers never learn the exact price of their phones because US providers so often bundle the phone cost into the monthly charge for cellular service, the average customer's cost for a phone is rapidly heading lower-from perhaps \$40 now to \$20 or so within two years. Add to these statistics the phones' growing capabilities.

They now, for example, in-

clude built-in cameras, can play streaming audio and video, and can download large data files at high speeds. They can also operate in wider geographic areas, which implies the ability to operate in multiple frequency bands. All these features add up to a huge testing problem: Before shipping any handset, the manufacturer must prove that all of these capabilities work correctly.

In production test, time is money. Fortunately, the test community recognizes that cell-phone test hasn't made optimal use of the test time. Some current test protocols waste seven-eighths of the

The 8960 one-box test set performs production testing of phones that support the  $1\times$  EV-DO Release A third-generation cellular-communication protocol and RF testing of such phones in R&D.

time. Several companies have developed ways to use this heretofore-wasted time. With the aid of new software, Agilent test equipment can increase the number of handsets it tests per unit of time by almost an order of magnitude. Agilent believes that it is the first company to offer such improvements. The company calls its 8960 the first onebox test set to perform production testing of phones that support the 1× EV-DO (evolution-data-optimized) lease A third-generation cellular-communication protocol and RF testing of such phones in R&D.

The term "1×" refers to one times the speed of TIA-EIA CDMA (code-division multiple access). The current speed of 1× EV-DO is approximately 2.4 Mbps downstream and 0.3 Mbps upstream. Over the next few years, these speeds and those of the competing HSPA (high-speed-packet-access) standard may increase by a factor of six.

Prices for the 8960 range from approximately \$45,000 to \$50,000, plus software. Including software, systems configured for production-test cost approximately \$50,000 to \$60,000, and those configured for R&D cost approximately \$80,000 to \$100,000.

# -by Dan StrassbergAgilent Technologies,www.agilent.com/find/8960.

www.agilent.com/find/8960, www.agilent.com/find/networkinabox.

#### **FROM THE VAULT**

"Your future has been changed. The advent of the MOS/LSI chipset microprocessors has catapulted you from lowly electron chaser to the heady heights of 'system architect.' You may not get any more money, but you'll be running some pretty big shows."

Robert H Cushman, former *EDN* special-features editor, Nov 5, 1973.

#### **DILBERT** By Scott Adams

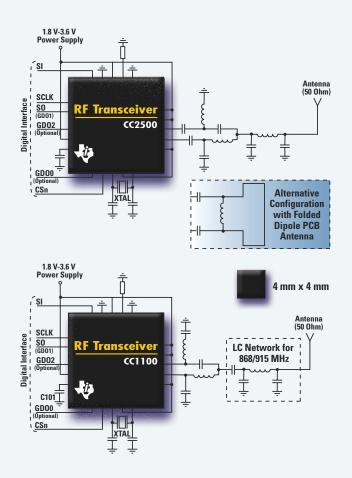

# 2.4 GHz and Sub-1 GHz RF ICs

## **Ultra-Low-Power, Small Footprint, Lowest System Cost**

The new **CC2500** and **CC1100** RF transceivers from Texas Instruments are the industry's lowest system cost, multi-channel radios for low-power wireless applications. Operating in the 2.4 GHz (CC2500) and sub-1 GHz (CC1100) frequency bands, the devices include several useful digital features like full packet handling, FIFO buffers, clear channel assessment, wake-on-radio and more.

- Wireless keyboard/mouse

- Automatic meter reading

- Wireless audio

- Alarm and security systems

- Home and building automation

#### ▶ Features

- Reference design with two-layer PCB with all components mounted on the same side

- Very small footprint: 4 x 4 mm, 20-pin QLP package

- Programmable data rate from 1.2 to 500 kbps

- Robust solutions with excellent selectivity and blocking performance

- Few external components

- Very low current consumption CC2500/CC1100:

- -Tx: 21.2/16.0 mA at 0 dBm

- R<sub>X</sub>: 13.3/15.2 mA at 250 kbps

- Pricing: \$1.75 in 1K

Low-Power RF Selection Guide Datasheets and Samples

www.ti.com/cc2500-1100 ° 800.477.8924, ext. 2500

Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1556A0

# DFM tools help with "lithography-friendly" layouts

entor Graphics claims that its latest DFM (design-for-manufacturing) offering will help IC designers make "lithographyfriendly" IC layouts. The company's new Calibre LFD (lithography-friendly design) is similar to a DRC/LVS (designrule-checking/low-voltagesignaling) tool. However, rather than check whether a layout conforms to design rules, such as trace widths and spacing, and early schematics, Calibre LFD checks whether a layout conforms to manufacturing-lithography rules that outline the dose and focus of a given manufacturing line. The tool incorporates the same engine as OPCVerify, a similar OPC (optical-proximity-correction) technology that Mentor introduced in January that targets lithography designers.

"Calibre LFD aims to capture process variation to improve design robustness," says Jean-Marie Brunet, productdevelopment manager for LFD products at Mentor. The company has devised the Calibre LFD kit, an encrypted format that allows fab facilities to pass lithography information to layout engineers who are using Calibre LFD. The kit includes manufacturer-defined recipe information and process models with optical processes, resist masks, and, in some cases, etch profiles. After loading the kit into Calibre LFD, layout engineers feed the tool their design layouts. The tool then outputs a set of DRC-like markers, flagging rule violations, which users then have to fix with a separate layout tool. The tool reports different types of error from those that DRC tools do.

The tool also produces a DVI (design-variability index), which helps users identify topologies that are sensitive to variability. The DVI also ranks topology problems to help users make trade-offs when they adjust their layouts or even tweak design rules. A layout modification may have a positive impact on timing and yield, but it can create a problem for power. "For layout en-

gineers to make an optimization, they need to have a reference point ... the ability to compare two layouts without requiring an in-depth understanding of lithography problems," says Brunet. Therefore, the tool assigns a DVI value to a given layout or even a piece of IP (intellectual property), and, the lower the DVI, the less susceptible the design is to variation across parameters.

Future releases of the tool will likely include features for fixing layouts. Mentor will maintain and update fab- and process-specific Calibre LFD kits as manufacturing processes at participating fabs evolve. The price for the tool starts at \$246,000 for a one-year subscription.

−by Michael Santarini▶Mentor Graphics, www.mentor.com.

# Process yields custom boards in five days

ardware developers are constantly under fire due to the excessive leadtimes between the start of a new project and hardware availability. It often takes months to design, lay out, fabricate, and debug a custom embedded-processor board with a unique set of peripherals that exactly fits the project. At the Embedded Systems Conference last month in San Jose, CA, Rabbit Semiconductor addressed that problem by announcing the innovative RabbitFlex process for creating and manufacturing customized boards.

Customers can go to the Rabbit Web site and create designs by choosing from an array of available board options, including Ethernet, RS- 232, RS-485, and RabbitNet, as well as analog- and digital-I/O circuits. All of these configurations reside in a customer-specific DesignID, which Rabbit then processes without NRE (nonrecurring-engineering) charges or set-up fees. A streamlined manufacturing process results in the production of custom devices that the factory builds and ships within five working days.

RabbitFlex offers a base level single-board computer powered by either the 51.6-MHz PowerCore 3800 or the 25.8-MHz PowerCore 3810. In addition to serial and digital options, customers can select from as many as 16 ADC channels or two DAC channels. RabbitFlex also supports a matrix keypad and

LCDs with or without back-lighting. The vendor's Dynamic C software-development system supports RabbitFlex, and programming requires an interface cable from the PC to a RabbitFlex connector. The process creates a unique Dynamic C library for each RabbitFlex board whose design reaches completion. Once a customer purchases a board, the library becomes finalized. Prices for the Rab-

bitFlex boards range from \$149 to \$279, depending on configuration. A RabbitFlex tool kit, supporting first-time development, sells for \$199 and includes a development-software package, product documentation, programming cable, and accessories. An optional display/keypad-accessory kit is available for \$69.—by Warren Webb

**▶Rabbit Semiconductor**, www.rabbitsemiconductor.com.

A new design-and-manufacturing process from Rabbit Semiconductor offers designers custom boards that the company automatically builds, tests, packages, and ships within five working days.

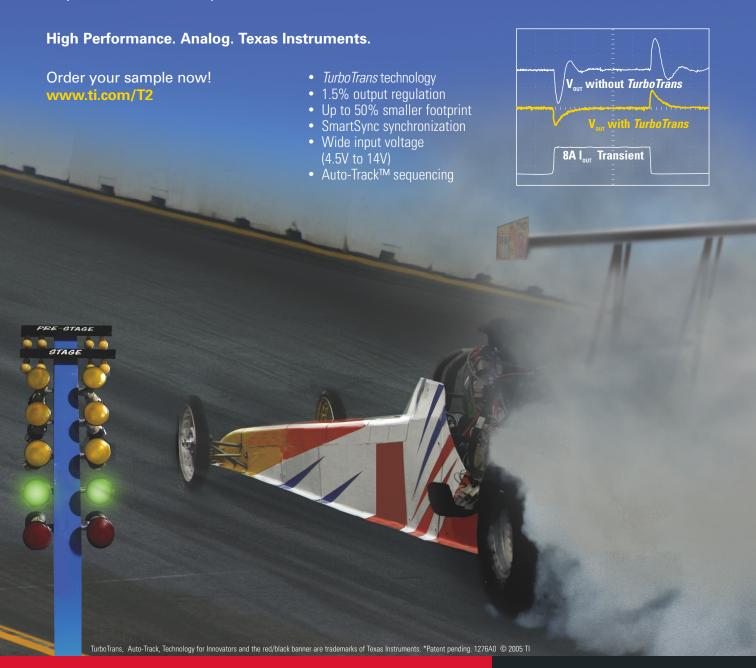

# Turbo Charge Your Transient Response

# with new T2 Power Modules & *TurboTrans*™

Tired of adding capacitors to your power design? Introducing the T2 series – the second generation PTH modules with *TurboTrans*™ technology. This patented\* technology provides up to an 8X reduction in required output capacitance while still meeting the stringent transient load requirements of DSPs, µPs, ASICs and FPGAs.

## **VOICES**

## Chandu Visweswariah:

# IBM innovation brings statistics to digital-IC design

handu Visweswariah, along with Kerim Kalafala, lead a team of R&D engineers at IBM Research and IBM Electronic Design Automation. Their small group recently won EDNs Innovator of the Year award for developing the EinsTimer statistical-timing tool, which also took top honors in the EDA Design and Implementation Tools category. Their group also won the Design Automation Conference's best-technical-paper award in 2004, and the company commercially released the

product before the Design Automation Conference in 2005.

# What is statistical-timing analysis, and what problems does it tackle?

Statistical-timing analysis traditionally handles process variations in a corner-based manner. In other words, the timer checks chip performance and timing relationships at various discrete "process corners." The main problems with this approach are that, in modern technologies, the number of corners can be large, and the technique does not lend itself to robust optimization. Statisticaltiming analysis models gate and wire delays as probability distributions with complex correlations and predicts chip performance and parametric yield as probability distributions. The advantages of the new paradigm include fast turnaround, incremental operation for optimization, pessimism reduction, sensitivity prediction, and enablement of performance-versus-yield trade-offs.

#### Analog designers are used to statistical proofs, but why does the digital world need them?

Digital designers relied on being able to bound their performance in a relatively straightforward way. But, now that wire delays play a larger role in determining performance and metal levels exhibit independent variations, it is no longer easy to bound performance. Because variability is a complex, multidimensional phenomenon, solid tool support is necessary to help circuit designers to maximize both parametric yield and performance.

# Why will the technology become important in the future?

As you move to 65-, 45-, and 32-nm processes, variability will only get worse. As you reach fundamental physical limits, you'll see the statistical nature of matter in dopant fluctuations,

oxide-grain boundaries, and line-edge roughness. Making individual worst-case scenarios of all these sources of variation will induce pessimism that will rob the new technologies of any performance gain. Besides, robust design and adaptive techniques will become more common. Hence, it is imperative that you embrace a statistical design-and-optimization methodology.

#### You said that launching the research program was difficult and required buy-in from management. What does management now think?

Management is enthusiastic! Any new paradigm generates resistance and inertia, particularly if a delay or arrival time is no longer a number but a probability distribution instead! However, with the right combination of generating results, persistence, and perseverance, statistical techniques are finding their way into mainstream use, including in IBM's ASIC tool kit. IBM is introducing these techniques in a phased manner, and they are invaluable parts of accurate timing with reduced pessimism and fast turnaround. Better process modeling couples with statistical timing to be the best way to achieve realistic timing results.

When IBM last year announced the tool, the company said it would offer it commercially to all comers and that it would be fab-independent. Is that still the case?

IBM has enabled Eins-Timer statistical timing in a fab-independent manner and has been working with a few clients in this mode. However, IBM's main focus is on providing comprehensive approaches to its technology and platform partners. Regardless of where customers fabricate their chips, IBM offers its clients design services that can take advantage of the company's knowledge and expertise, including statistical timing and optimiza-

# What are the next steps for the technology? How do you proliferate the technology and get designers not only up to speed on its benefits, but also able to use it on real designs?

Several parts of the A methodology must evolve to take full advantage of the new statistical paradigm: process modeling, library characterization, physical synthesis, and test. Several factors contribute to quick proliferation. First, the tools must be pushbutton and easy-to-use. Second, the timing reports should be intuitive and configurable so that someone schooled in deterministic timing will easily get used to the new reports. Finally, training, education, support, and documentation will play big roles in widespread acceptance of the new tools.

-by Michael Santarini

# Outstanding RF performance—at outstanding prices. In power detection, analog is everywhere.

#### AD8317

- · Operating 1 MHz to 10 GHz

- 50 dB dynamic range

- Better than  $\pm 0.5$  dB stability over temperature

- 3 mm × 2 mm, 8-lead LFCSP

- Pricing: \$3.93/1k USD

#### AD8318

- Operating 1 MHz to 8 GHz

- 60 dB dynamic range

- Better than ±0.5 dB stability over temperature

- 4 mm × 4 mm, 16-lead LFCSP

- Pricing: \$4.99/1k USD

#### AD8319

- Operating 1 MHz to 10 GHz

- 40 dB dynamic range

- Better than ±0.5 dB stability over temperature

- 3 mm  $\times$  2 mm, 8-lead LFCSP

- Pricing: \$2.99/1k USD

# New log amps extend RF power measurement to 10 GHz

ADI's new log amps redefine the parameters of accurate RF power detection. These detectors support all cellular and broadband wireless standards and other demanding applications up to 10 GHz—enabling designers to address more applications with less time and effort. They also provide performance and value that are unsurpassed in the industry.

From RF to IF, mixers to power detection, for handsets to base stations—analog is everywhere.

#### ADI—for every part of RF designs

- VGAs

- Modulators

- Demodulators

- Mixers

- Gain blocks

- · RF amplifiers

- DDS

- PLL

To order samples and evaluation boards, visit our website.

#### **AGLOBAL DESIGNER**

## MEMS microphone has digital output

kustica's claim that its AKU2000 is the first CMOS MEMS (microelectromechanical-system), direct-digital-output, single-chip microphone. The company licensed the technology, which it believes is comprehensively patent-protected, from Carnegie-Mellon University (Pittsburgh). The technology allows Akustica to build MEMS using the metallization layers of a standard-CMOS process to form the membrane that

makes the sensing element of the microphone. Because the technology is standard-CMOS, the company can build an output amplifier and fourth-order sigma-delta modulator onto the same chip.

Unlike the electret-capacitor-microphone technology the Akustica product aspires to replace, the chip is surfacemountable in a standard flowsoldering process. It requires a clock input of 1 to 4 MHz and operates from 2.8 to 3.6V, us-

#### Spin-coating process produces TFT with liquid silicon

Seiko Epson Corp and JSR Corp have jointly developed a silicon film with liquid coating and ink-jet-patterning processes. The silicon film produces a low-temperature polysilicon TFT (thin-film transistor) with performance comparable to that of film using the conventional CVD (chemical-vapor-deposition) method. The new material is a high-order silane compound of hydrogen and silicon that dissolves in an organic solvent.

To get a silicon film, developers spin-coated the material onto a substrate and baked it in an inert atmosphere. The electrons in the process achieve mobility of 108 cm<sup>2</sup>/Vsec. Forming a TFT prototype using a silicon-film pattern with the ink-jet method achieves mobility of 6.5 cm<sup>2</sup>/Vsec, a better figure than that for spin-coating. Eventual target applications include LCD televisions and ink-jet printers.-by Tatsuya Ito, EDN Japan

- Seiko Epson Corp, www.epson.co/jp.

- **⊳JSR Corp**, www.jsr.co/jp.

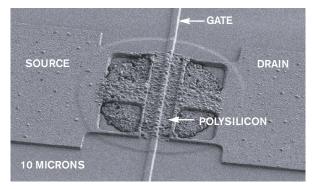

A scanning electromicroscope photo of a sample of Epson's new film coating shows the source, gate, drain, and polysilicon island.

ing less than 750 μA. Akustica designed the 4×4-mm package for reflow soldering on the reverse of a pc board. The board must have a throughhole aligned with the membrane opening on the chip, but this arrangement simplifies sealing the assembly to an external surface. The output is a pulse-density-modulated, serial bit stream. Akustica defines the chip's frequency response by a mask that specifies it to be ±3 dB over 200 Hz to 6 kHz.

Akustica initially targets the laptop/notebook-computer market, although the cellular phone is a potentially bigger market. However, the company believes that the standard electret-capacitor microphone is more deeply entrenched in cell phones and that Akustica will be better able to attack that sector when it has driven its product further down the price curve.

The fact that the device has a digital output makes the AKU2000 of great interest to laptop/notebook designers and also those working in a similar physical format. The high impedance and low signal level of an electret make it vulnerable to electrical noise: It is difficult to route screened wiring through a laptop's hinge, so the microphone often resides in the chassis of the machine, close to sources of mechanical noise, such as harddisk drives and fans. The device's digital output not only overcomes that problem, but also makes it feasible to mount two or four of them on a screen bezel. The designer can use them as a small array to shape the overall acoustic response into a high-sensitivity zone where the user is and cancel out noise from elsewhere. The AKU2000 sells for \$3.87 (1000).

> -by Graham Prophet, EDN Europe

>Akustica, www.akustica.

#### Consortium invests \$800,000 for five years

The JEITA (Japan Electronics and Information Technology Industries Association) has announced a new semiconductor-development project, TSC (Tsukuba Semiconductor Consortium). It combines the STARC (Semiconductor Technology Academic Research Center) design-technology company and Selete (Semiconductor Leading Edge Technologies). STARC plans to invest 20 billion yen (\$180,000) for five years, and Selete will invest 70 billion yen (\$600,000) for five years. Both focus on chip-technology development in process nodes of 45 nm and smaller.

STARC will focus on design for manufacturing, high-level design, and failure diagnostics, and Selete will target metal-gate processes, high-k-gate processes, carbon interconnect, extreme-ultraviolet lithography, and optical interconnect-by Takatsuna Mamoto, EDN Japan

- **Japan Electronics Information Technologies** Industries Association, www.jeita.or/jp.

- **Semiconductor Technology Academic Research** Center, www.starc.jp/index-e.html.

- Semiconductor Leading Edge Technologies, www.selete.co.jp/?lang=EN.

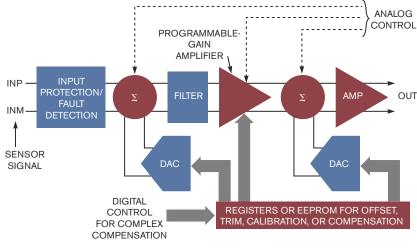

## A series of engineering insights by Analog Devices.

# Highly Integrated, Programmable Single-Component Sensors Solve Problems in Industrial System Design

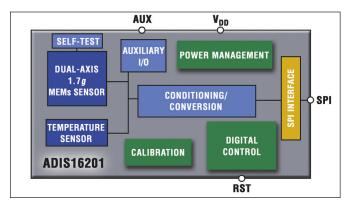

Sensors have the potential for providing revolutionary improvements in performance, reliability, safety, and cost-of-ownership within industrial system designs. Examples involving inertial sensors include platform stabilization, motion control for industrial machinery, security devices, antenna stabilization, robotics, navigation, mechanical leveling, and many others. However, a gap has long existed between good sensor technology and its implementation within critical industrial systems. Embedding sensor processing within industrial equipment typically requires that the designer have intimate knowledge of the sensor technology to design and implement a signal chain that properly tunes and calibrates a given sensor for its application. For inertial sensors, this typically also requires the capability for motion testing. The system expense of this implementation has created a barrier to more rapid sensor deployment, particularly for customers and applications with moderate production volumes. The problem is worsened by the physical limitations posed by some applications (for instance, embedded vibration analysis) where extreme density, environmental conditions, and remoteness have pushed requirements beyond what is available in standard sensor and signal conditioning components.

The Analog Devices' iSensor™ product family was created in recognition of this gap in industrial sensor applications. The ADIS16201 iSensor is the first implementation of a new patent pending single-package integration technology. It's the world's first direct output, linear-in-degrees inclinometer that is available as a single component. Incorporating a complete sensor and data processing signal path, the device is both a fully functional programmable dual-axis accelerometer and a dual-axis inclinometer.

A complete dual-axis acceleration and inclination angle measurement system in a single, compact package.

The ADIS16201 provides a gain and offset variability of less than 1%, reduces voltage and mechanical mounting sensitivities, and provides a simple single command interface which allows in-system auto-zero calibration.

It also includes several embedded features, including programmable sample rate, digital filtering, power management, configurable alarms, auxiliary analog and digital I/O, and self-test. This eliminates the need for external circuitry and enables a much simplified system interface, all controlled via an SPI port. Sensor outputs include two axes of  $\pm 1.7~g$  acceleration, two axes of  $\pm 90^\circ$  inclination (with accuracy within 0.25°), and temperature. Previously, the same functionality and performance could only be found in devices more than  $100\times$  larger, and  $10\times$  more costly. The ADIS16201 is available in a small 16-lead laminate-based land grid array (LGA) package, at 1k unit pricing of \$28.

With up to 100x size reduction and 10x cost reduction, the ADIS16201 brings embedded sensing to a broader base of customers and applications.

iSensor integration eliminates a key barrier to the advancement of sensor applications in the industrial market by offering unprecedented functionality, programmability, and simplicity to the system designer. The standard programming interface also allows the user to easily tailor the devices to the application, and very quickly move through prototyping, evaluation, and implementation. Now in development are additional iSensor products targeted at embedded vibration analysis and programmable angular rate sensing. For additional product information, visit www.analog.com/iSensors. ▶

Author Profile: **Bob Scannell** is the business development manager for the iSensor product strategy at Analog Devices.

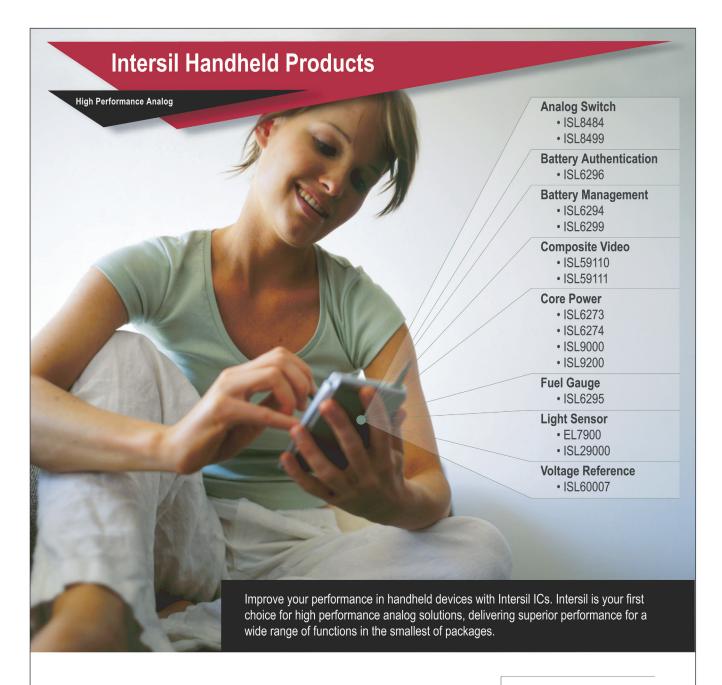

- Analog Switches

- Battery Management

- Battery Authentication

- Composite Video Drivers

- Core Power

- DCPs

- Image Buffers

- Ambient Light Sensors

- Memory Power Mangement

- Voltage Reference

Intersil's innovative handheld products include everything form complete power management to an ultra-small video driver that enables high-quality video output directly from a handheld device. We've even got backlight and ambient light sensors that combine efficient power usage along with superior usability and display.

To see all the different functions Intersil supports in handheld products go to www.intersil.com/applications and see the latest high-end consumer application block diagrams available.

Complete Handheld Products Linecard is available at www.intersil.com/handheld

B

1001 Murphy Ranch Road, Milpitas, CA 95035 North America 1-888-INTERSIL International (01) 1-321-724-7143

#### BY BONNIE BAKER

# Charge your SAR-converter inputs

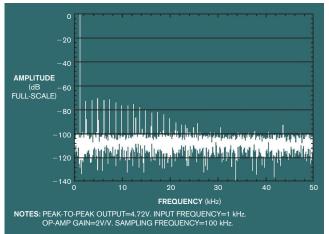

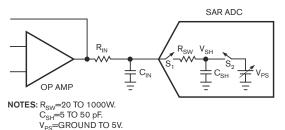

t is tempting to drive a SAR (successive-approximation register) ADC with just an amplifier. As an added benefit, you might try to configure the amplifier circuit in a gain or antialiasing-filter stage. These enhancements seem reasonable as you try to optimize your device use. However, did you think about whether you would compromise the effectiveness of your op-amp/converter pair (Figure 1)?

If you need good, accurate performance at dc as well as ac, regardless of your throughput rate, the analog-input stage of the SAR ADC requires special attention. The model of the input stage of most modern ADCs is a resistor/capacitor pair with two switches and a voltage source (**Figure 2**). The resistance,  $R_{\text{SW}}$ , in the converter's input is the closed-switch resistance. This switch

closes during the acquisition time of the conversion process and opens during the conversion time. The converter uses capacitance,  $C_{\rm SH}$ , which is the total of the distributed on-chip capacitance, for the input-signal-sampling process.

First and foremost, you need to give sample capacitor  $C_{\rm SH}$  enough charging time to reach at least  $^1\!\!/_2$  LSB of the final value. Theoretically, for a 12-bit con-

Figure 1 An improperly driven, 12-bit SAR ADC can produce unwanted noise and harmonic distortion. In this diagram, the SNR (signal-to-noise ratio) is 69.76 dB full-scale, and the THD (total harmonic distortion) is —63.34 dB full-scale for a converter that performs at an SNR of 71.82 dB full-scale and a THD of 78.82 dB full-scale.

Figure 2 The input structure of a SAR converter initially has a sample-and-hold capacitor, C<sub>SW</sub>, following a switch, S<sub>1</sub>, which controls the sampling time.

verter, enough time would be more than eight times  $R_{\rm SW} \times C_{\rm SH}$ . Given error margins and component variations, you should use multiples of 10 to 15. The SAR converter needs an op amp with a gain of  $\pm 1 \text{V/V}$ , along with an  $R_{\rm IN}$ - $C_{\rm IN}$  external resistor/capacitor pair. During sampling, the ADC uses capacitor  $C_{\rm IN}$  for signal stability. Resistor  $R_{\rm IN}$  isolates the amplifier from the ADC's load capacitance. The op amp isolates the ADC from high-impedance loads and drives  $C_{\rm IN}$  and  $C_{\rm SH}$ , facilitating a quick charge time while the ADC is sampling.